- 品牌

- FCom富士晶振

- 型号

- FCO-L-PG

- 系列

- FCO-L-PG

- 类型

- MHz晶体

- 频率范围

- 10 MHz ~ 220 MHz

- 工作电压

- 1.8V / 2.5V / 3.3V 可选

- 温度频差

- ±25ppm / ±50ppm(出厂可选)

- 工作温度

- –40°C ~ +105°C

- 相位抖动

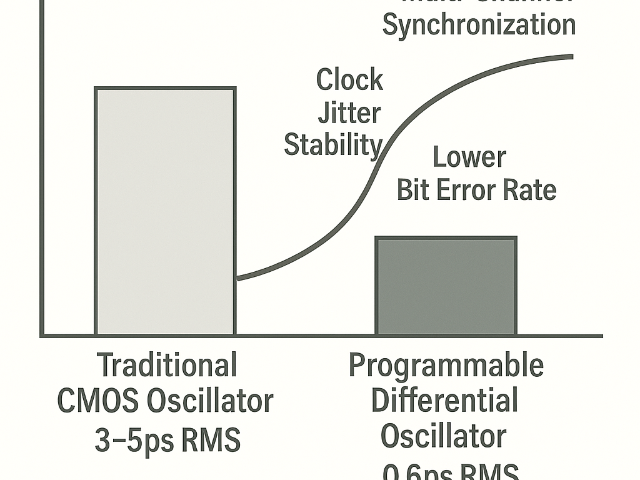

- 0.2 ~ 0.6ps RMS(12kHz~20MHz)

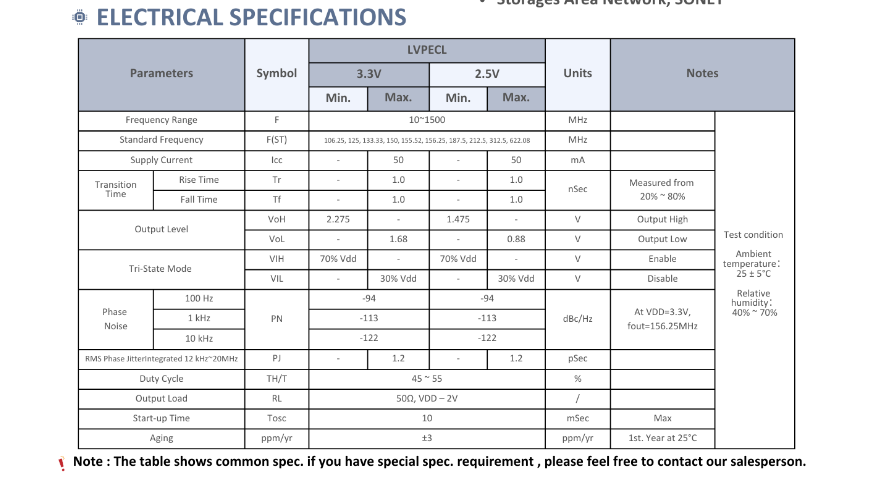

网络交换芯片中的时钟冗余与接口兼容性 现代网络交换芯片集成高速交换矩阵、MAC层接口、PHY收发单元、管理总线与SDRAM控制器等复杂模块,通常需配置多个时钟输入用于控制数据通道频率与同步延迟。FCom富士晶振的可编程差分振荡器具备灵活配置频率与接口的能力,为千兆/万兆/百兆多速率交换系统提供精密时钟保障,并兼顾可靠性冗余机制。 网络交换设备中,不同端口速率(如1G/2.5G/10G/25G/40G)需要对应不同参考频率,如25MHz、50MHz、100MHz、156.25MHz、312.5MHz等。传统振荡器需针对不同端口配置多个器件,FCom可编程振荡器通过一次预设或远程配置即可支持多个频率输出需求,极大地减少器件数量与BOM复杂度。未来模块化时钟系统将采用可编程差分振荡器方案。超宽温可编程差分振荡器单价

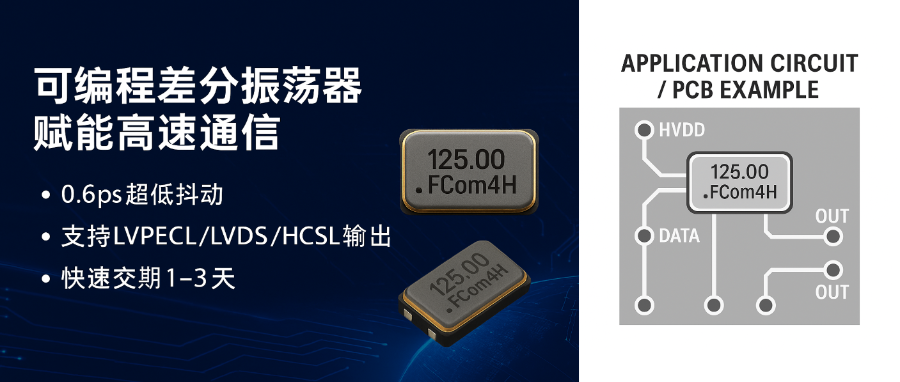

可编程差分振荡器

CXL互联平台对多频可编程振荡器的灵活性需求 CXL(Compute Express Link)作为下一代高速互联协议,支持处理器与内存、加速器、存储设备之间的高带宽、低延迟连接。在CXL 2.0/3.0系统中,不同子模块可能使用频率源,而参考时钟的精度、接口电平、启用逻辑要求高度可定制。FCom富士晶振推出的可编程差分振荡器正好满足此类平台对时钟配置灵活性与性能稳定性的双重要求。 CXL互联链路中常用频点包括100MHz、133.33MHz、156.25MHz与200MHz,对应不同的PHY与互联层架构。FCom可编程振荡器允许通过电编设定频率、接口标准与启停控制,使同一器件可支持CXL主控芯片、桥接控制器、内存池接口等多个时钟需求。 特别是在模块化CXL架构中,FCom产品支持三态控制输入(OE/EN),便于在多个计算节点之间进行主从时钟切换,增强集群级同步策略的灵活性。通过0.1ps以内抖动指标,其输出信号完全满足CXL高频SerDes收发系统的误码率要求。优势可编程差分振荡器订做价格从频率配置到接口兼容,可编程差分振荡器各个方面支持。

量子计算控制平台的超高稳定时钟参考 量子计算平台的控制系统通常包含精密的激励脉冲生成器、量子位读出电路、锁相环管理、超导器件驱动与同步ADC/DAC模块,其性能高度依赖低噪声、高稳定、可定制的时钟系统。FCom富士晶振可编程差分振荡器通过数字调控机制与极限低抖动特性,在量子计算控制系统中提供高一致性、低失调的时钟基准。 该系列支持10MHz~250MHz频率自定义,输出接口为LVPECL或LVDS,满足主控FPGA、射频控制器、高速模数转换链路的同步与触发要求。其0.05ps RMS抖动性能可大限度降低量子比特激励干扰,提高相干时间与读出准确率。 产品支持OTP频率写入、主控动态频率设置与片上冗余输出切换,适合多通道并行操作的实验级平台部署。 其高可靠封装设计通过静电保护与热漂抑制测试,在实验室冷却腔体、高温合成器与电磁屏蔽仓环境下均可稳定工作。目前该器件已在国内多家量子实验室与商业量子计算平台中完成关键试验验证。

工业自动化控制台对冗余时钟管理的刚性需求 现代工业控制系统正迈向分布式、可编程、智能协同的体系结构,各类现场控制台如PLC、人机界面(HMI)、IO扩展模块、运动控制器、SCADA前端等在多个系统冗余通信、联动判断逻辑中对时钟系统提出新的结构性挑战。FCom富士晶振可编程差分振荡器因其灵活可控、低功耗、抗干扰等特性,成为工业控制台中冗余时钟管理的关键部件。 FCom器件支持通过I²C或出厂配置实现多通道输出控制,适配主控芯片、以太网接口、CAN总线驱动、Modbus RTU中继芯片等多个逻辑时钟域。其三态逻辑输出控制可实现主-备时钟切换、通道快速故障隔离,并通过硬件管脚配置提升系统可靠性。 产品封装支持3225至7050,输出频点如25MHz、50MHz、100MHz、125MHz、200MHz等,均可通过配置器件灵活选定,适合工业自动化系统升级、多型号兼容部署。 其抗干扰能力经EN 61000工业级测试验证,频率稳定性优于±10ppm,适用于高压场站、智能变电所、化工厂、钢铁流水线等复杂现场控制场景。多通道通信系统依赖可编程差分振荡器保持时序一致。

工业级多节点同步系统对时钟精度的结构化依赖 工业自动化中如机械臂协调、智能输送系统、多传感器采集平台中,多个处理节点需依赖统一、低延迟、抗干扰的时钟源来维持任务同步。FCom富士晶振推出的可编程差分振荡器,为这种分布式控制系统提供精确、灵活、低抖动的同步时钟解决方案。 通过配置支持25MHz、50MHz、100MHz、125MHz、156.25MHz等频率输出,并兼容LVDS、HCSL等差分格式,可为以太网通信芯片、传感器接口模块、控制器之间建立统一频率框架。每个时钟输出通道均可配置启停逻辑与OE控制,从而在任务切换中进行动态时钟管理。服务器主板推荐采用可编程差分振荡器简化BOM。高频可编程差分振荡器订做价格

可编程差分振荡器已成为前沿通信平台的标准配置。超宽温可编程差分振荡器单价

大规模FPGA设计项目中的统一时钟架构构建 在通信基站、图像处理平台、测试测量设备、AI网关等多个场景中,FPGA作为关键处理单元需同时管理多个时钟域(输入同步、IO驱动、PLL控制、AXI总线),设计中存在频率出错、资源浪费与同步偏移风险。FCom富士晶振可编程差分振荡器提供统一频率源与灵活配置方式,为大规模FPGA设计提供集中管理的可控时钟结构。 FCom产品支持多频输出(如24MHz、50MHz、100MHz、125MHz、156.25MHz、200MHz),具备LVDS/HCSL多接口配置能力,可连接至FPGA外部时钟输入口、IO Bank参考时钟、PLL Clock-IN与内部逻辑触发器。输出抖动低至0.1ps,保障时序余量。 通过FCom提供的GUI工具,用户可快速配置目标频率组合并仿真接口兼容性,提升工程调试效率。产品支持1.8V~3.3V工作平台,适应不同FPGA品牌(Xilinx、Intel、Lattice、Microchip等)IO电压标准。超宽温可编程差分振荡器单价

- 优势可编程差分振荡器工厂直销 2025-05-27

- 高性能可编程差分振荡器批量定制 2025-05-26

- 工业级可编程差分振荡器联系方式 2025-05-26

- 超宽温可编程差分振荡器订做价格 2025-05-25

- 本地可编程差分振荡器供应商 2025-05-25

- FCO-3L-PG可编程差分振荡器供应商家 2025-05-25

- 低功耗可编程差分振荡器批量定制 2025-05-25

- 低抖动可编程差分振荡器工厂直销 2025-05-25

- 5032可编程差分振荡器推荐厂家 2025-05-25

- 国产可编程差分振荡器常用知识 2025-05-25

- 可编程差分振荡器答疑解惑 2025-05-25

- 3225可编程差分振荡器有哪些 2025-05-25